微細化に頼らずに記憶容量を拡大するという裏技

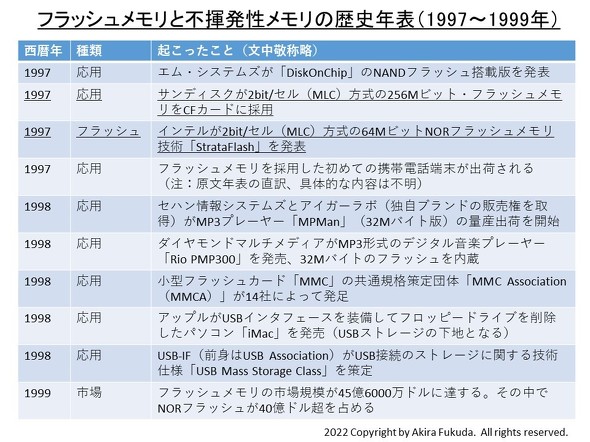

フラッシュメモリに関する世界最大のイベント「フラッシュメモリサミット(FMS:Flash Memory Summit)」の会場では最近、「Flash Memory Timeline」の名称でフラッシュメモリと不揮発性メモリの歴史年表を壁にパネルとして掲げていた。FMSの公式サイトからはPDF形式の年表をダウンロードできる(ダウンロードサイト)。

この年表は1952年〜2022年までの、フラッシュメモリと不揮発性メモリに関する主な出来事を記述している。本シリーズではこの歴史年表を参考に、主な出来事の概略を説明してきた。原文の年表は全て英文なので、これを和文に翻訳するとともに、参考となりそうな情報を追加した。また年表の全ての出来事を網羅しているわけではないので、ご了承されたい。なお文中の人物名は敬称略、所属や役職、企業名などは当時のものである。

前回は、世界で初めてMP3方式の携帯型オーディオプレーヤーを試作したドイツのオーディオ開発ベンチャー「ポンティス(Pontis)」について述べた。時期は1995年〜2005年である。今回と次回は、フラッシュメモリが製品に「多値記憶技術(1個のメモリセルに2ビット以上のデータ(論理値)を格納する技術)」を駆使し始めた状況を前後編でご紹介する。時期は1997年〜2001年である。

1990年代のフラッシュメモリに課せられた最大の使命は、記憶容量を急速に拡大することによってビットコスト(記憶容量当たりの製造コスト)を下げ、DRAMよりも低いビットコストで市場に供給することだった。言い換えると1990年代のフラッシュメモリは、DRAMよりも高価なメモリにとどまっていた。

シリコンダイ当たりの記憶容量を拡大する主要な手段は、微細化(加工寸法の縮小)である。微細化の恩恵を受けるのは、DRAMも同様だ。すなわち、微細化だけではDRAMになかなか追い付けない。DRAMとは異なるビットコスト低減手法として考案されたのが、1個のメモリセルに2ビット以上のデータを記憶する技術である。1997年にインテルが「StrataFlash(ストラータフラッシュ)」の名称でNORフラッシュメモリに導入したのが始まりだ。

インテルの私設博物館「インテルミュージアム」(米国カリフォルニア州サンタクララ)に展示された「StrataFlash」技術のNORフラッシュメモリ(左)と説明文(右)。2017年6月18日に筆者が撮影したもの[クリックで拡大]

インテルの私設博物館「インテルミュージアム」(米国カリフォルニア州サンタクララ)に展示された「StrataFlash」技術のNORフラッシュメモリ(左)と説明文(右)。2017年6月18日に筆者が撮影したもの[クリックで拡大]NORフラッシュメモリから実用化が始まる

インテルが初めて実用化した多値記憶技術は、1個のメモリセルに2ビットのデータを記憶する技術である。一般的には「MLC(Multi-Level Cell)」技術と呼ばれている。製品の記憶容量は64Mビットである。物理的なメモリセルの数は32Mビットと等しい。MLC技術によって64Mビットのデータを記憶する。つまり、同じシリコンダイで記憶容量を2倍に増やしている。

2ビットのデータを1個のメモリセルに記憶させる手法は単純だ。3段階のしきい電圧を書き込み(プログラム)、読み出すだけである。消去(イレーズ)動作のしきい電圧と併せて4段階のしきい電圧を有するので、2ビット(4値)のデータを記憶できる。

手法は単純だが、実際の製造は容易ではない。1ビット(2値)を読み書きする従来技術と比べ、しきい電圧のマージン(余裕)は約3分の1と大幅に減ってしまう。しきい電圧の精密な制御が書き込み動作で必要となるのはもちろんのこと、10年のデータ保持期間を従来の3分の1しかないマージンで保証することが求められる。

それでもインテルは、MLC技術をNORフラッシュメモリ製品に積極的に導入していく。2001年には記憶容量を256Mビットに拡大した製品を発表した。同じ年には、NANDフラッシュメモリでも多値記憶技術の導入が始まった。

(後編に続く)

⇒「福田昭のストレージ通信」連載バックナンバー一覧

からの記事と詳細 ( 多値記憶(マルチレベル)時代の始まり(1997年~2001年)(前編) - EE Times Japan )

https://ift.tt/s6TQGvb

No comments:

Post a Comment